一、等离子屏X、Y电极驱动波形的产生:

前面几部分已经把等离子屏的构造;基本工作原理作了介绍了,特别是第三讲的;驱动等离子像素放电腔体的:初始化、寻址、维持放电、擦除这四个过程,可以看出等离子像素放电腔体的主要工作过程;完全依靠所施加在X电极、Y电极和地址电极上的驱动脉冲来完成的;如图1所示。X电极、Y电极和地址电极分别有各自的驱动脉冲,这三个独立的驱动脉冲在时间上又有严格的对应关系。

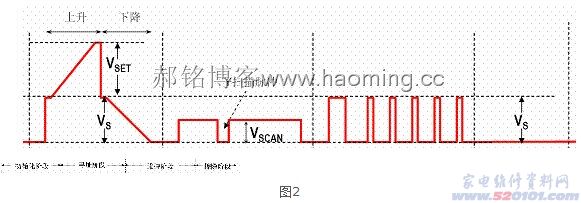

各驱动脉冲的波形在波形上、幅度上、时间上都有严格的定量要求;否则等离子屏不能正常工作。我们以Y电极驱动波形为例,图2所示是Y电极的驱动波形图;

从图2的Y电极驱动波形中可以看出;在 初始化、寻址、维持放电、擦除这四个过程中,每一个时间段;波形不同、时间不同、振幅不同。而且要求要有极高的精度;驱动脉冲的时间要求精确在微秒级以内,幅度要求;其电压(振幅)的误差在±1V以内。

Y驱动脉冲的波形中有三个电压;Vs Vset Vscan 精度要求都在±1V以内,例如国外某一品牌的等离子屏的Y电极驱动波形的Vset 就要求为170V 正负误差在1V以内;Vscan要求70V正负误差也在1V以内,Vs为110V正负误差也在1V以内(为了方便维修在等离子屏的电路板上,都贴有一个不干胶的标签;表明各电压的幅度值及误差要求);并且在初始化阶段的两个斜坡(上升、下降斜坡)的倾斜度都有严格的要求;并且在电路上要做到斜坡的可调(第三讲的图2、图3所示)。

这么复杂的波形、这么高要求;是怎么来的?由什么电路提供的?

这就是一直困扰着某些维修人员;感觉到学习等离子维修技术难以逾越的障碍——等离子逻辑驱动电路的Y驱动电路提供的。(等离子逻辑驱动电路包括逻辑板电路、Y驱动板电路、Y上下扫描板电路、X驱动电路和地址驱动电路,这些就是等离子屏显示的核心技术(难度较高),理解了、熟悉了、掌握了、能分析电路原理了,在你的维修生涯就是一个巨大的飞跃)。

Y驱动电路实际上就是:众多的开关组合,这些开关就是大功率的MOS开关管,这些开关管在逻辑板电路送来的控制信号的作用下;相应的动作;最后输出了我们需要的Y电极驱动脉冲。

下面以一系列图片说明Y驱动波形产生的过程及条件:

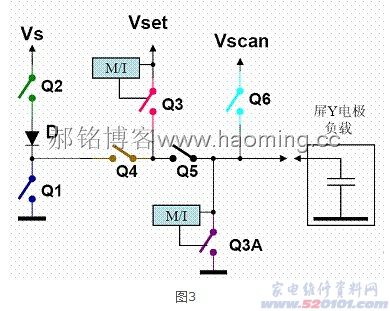

图3所示;是一个产生Y电极驱动脉冲(波形)的组合开关电路的等效电路图

在图3中主要由Q1、Q2、Q3、Q3A、Q4、Q5、Q6七个开关组成的一个开关组合电路;图中;“屏Y电极负载”代表等离子屏的Y电极(因为等离子屏的负载特性呈容性,内部以一个电容器符号代表),上面的Vs、Vset、Vscan是由开关电压提供的稳定的直流电压(某一款进口等离子屏为例:Vs=110V、Vset=170V、Vscan=70V),要求误差为;±1V。

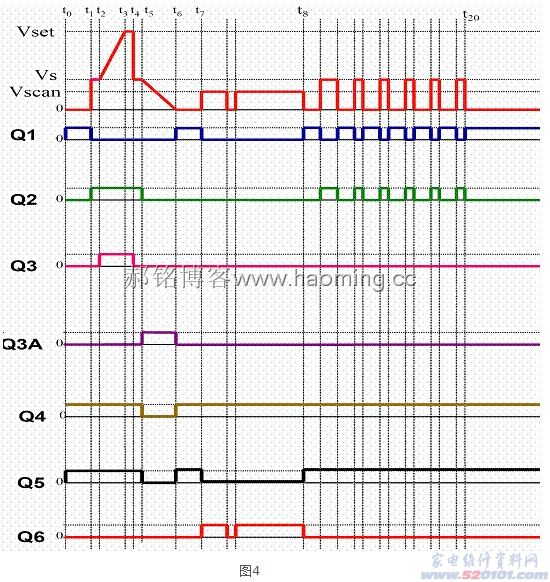

图3中的Q3、Q3A两只开关,带有“M/I”符号;表示该开关在接通时内阻是由大到小逐步减小最后彻底导通,导通电流是由小到大变化(实际电路的Q3及Q3A是MOS管加反馈电路来实现)。控制Q1、Q2、Q3、Q3A、Q4、Q5、Q6这七个开关的激励控制信号如图4所示;图4中的Q1、Q2、Q3、Q3A、Q4、Q5、Q6七条激励波形图就是图3中Q1、Q2、Q3、Q3A、Q4、Q5、Q6这七个开关的激励控制信号,(这七个激励信号,由等离子屏的逻辑板电路产生)。

图4上面的Y电极驱动波形是由下面的激励信号产生的(注意图4下面的激励波形和上面Y电极驱动波形在时间上的对应关系)。

图3的开关组合的供电压是Vs、Vset、Vscan,各个开关在激励信号的控制下;相应的“导通”、“断开”在输出端(屏负载);就输出规定要求的Y电极驱动信号(波形)。

二、Y电极驱动波形产生的过程:

1、 t0~t1时间:图4中的t0~t1 时间段 Y驱动波形;零电平

此期间;Y驱动组合开关电路工作状态如图5所示:

图5中 右边是在t0~t1时间;图中阴影部分所示;在这个时间段;可以看出Q1、Q4

、Q5激励信号是高电平,高电平就表示开关闭合导通;其它的Q2、Q3、Q3A、Q6激励波形是低电平,低电平就表示开关开路断开;对应左边的组合开关图中的开关;Q1、Q4、Q5是导通状态。其它的开关Q2、Q3、Q3A、Q6是断开状态。

Q1导通接地、Q4、Q5导通,等于此时t0~t1时间段;输出加到屏负载是零电平。

图5右边;可以看到上面Y驱动波形在这个时间段为:“零”。

2、 t1~t2时间:这个时间段是初始化时间段内部的Vs平台;幅度为:Vs

此期间;Y驱动组合开关电路工作状态如图6所示:从图6右边的 t1~t2时间阴影部分可以看出:可以看出Q2、Q4、Q5激励信号是高电平;Q2、Q4、Q5闭合导通;其它的Q1、Q3、Q3A、Q6激励波形是低电平;对应左边的组合开关图中的开关;Q2、Q4、Q5是导通状态。其它的开关Q1、Q3、Q3A、Q6是断开状态。Q2导通等效于Vs电压经过 Q2、二极管、Q4、Q5输出到屏负载;Y电极驱动波形在这个时间段为:Vs”。

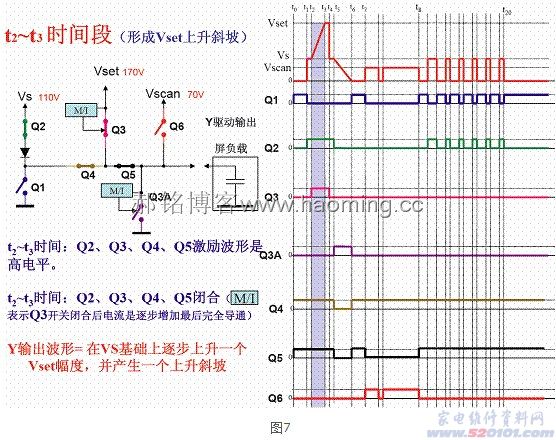

3、 t2~t3时间:这个时间段是Vset上升的斜坡段,波形的特点是:由Vs幅度逐步上升到Vset幅度;形成一个上升斜坡。

此期间;Y驱动组合开关电路工作状态如图7所示:从图7的右边 t2~t3时间阴影部分可以看出,此时:Q2、Q3、Q4、Q5激励信号是高电平;对应左边的组合开关图中的开关;Q2、Q3、Q4、Q5闭合导通;其它的Q1、Q3A、Q6激励波形是低电平;对应左边的组合开关图中的开关; Q1、Q3A、Q6是断开状态。Q3导通等效于把Vset电压加到输出端(由于二极管的存在,Vset不会倒灌到Vs),因为Q3是一个具有“M/I”功能的开关(导通时:电流只能逐步增大),所以;输出电压只能由Vs平台逐步上到Vset幅度,形成一个斜坡。输出到屏负载;Y电极驱动波形在这个时间段为:由Vs幅度逐步上升到Vset幅度的斜坡。

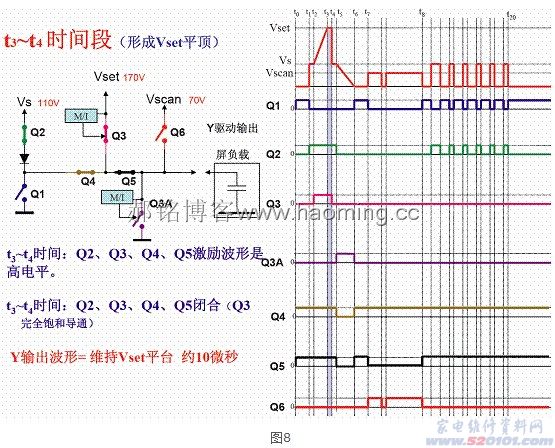

4、 t3~t4时间:这个时间段是Vset平顶阶段;波形的特点是:维持约10微秒Vset幅度的一个平台。

此期间;Y驱动组合开关电路工作状态如图8所示:从图8的右边 t3~t4时间阴影部分可以看出,此时:Q2、Q3、Q4、Q5激励信号是高电平;对应左边的组合开关图中的开关;Q2、Q3、Q4、Q5闭合导通;其它的Q1、Q3A、Q6激励波形是低电平;对应左边的组合开关图中的开关; Q1、Q3A、Q6是断开状态。现在Q3已经彻底导通;等效于把Vset电压加到输出端(由于二极管的存在,Vset不会倒灌到Vs),输出到屏负载;Y电极驱动波形在这个时间段为:10微秒时间Vset幅度的平台。

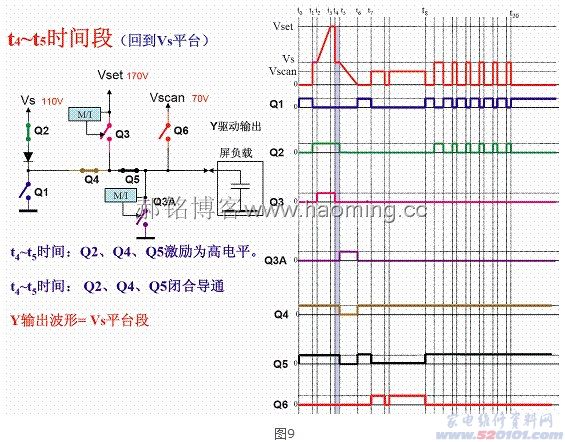

5、 t4~t5时间:这个时间段是由Vset回到Vs平台;幅度为:Vs

此期间;Y驱动组合开关电路工作状态如图9所示:从图9右边的 t4~t5时间阴影部分可以看出:可以看出Q2、Q4、Q5激励信号是高电平;Q2、Q4、Q5闭合导通;其它的Q1、Q3、Q3A、Q6激励波形是低电平;对应左边的组合开关图中的开关;Q2、Q4、Q5是导通状态。其它的开关Q1、Q3、Q3A、Q6是断开状态。输出的Y电极驱动波形在这个时间段为:Vs

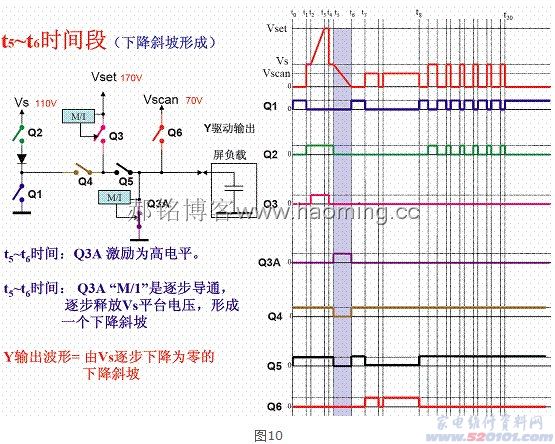

6、 t5~t6时间:这个时间段是下降斜坡段;波形的特点是:由Vs平台逐步下降为零。

此期间;Y驱动组合开关电路工作状态如图10所示:从图10的右边 t5~t6时间阴影部分可以看出,此时:只有Q3A激励信号是高电平;对应左边的组合开关图中的开关;Q3A闭合导通;其它的Q1、Q2、Q3、Q4、Q5、Q6激励波形是低电平;对应左边的组合开关图中的开关;Q1、Q2、Q3、Q4、Q5、Q6是断开状态。因为Q3A也是一个具有“M/I”功能的开关(导通时:电流只能逐步增大),这样Q3A的导通逐步的把容性负载存储的电荷逐步释放,致使电压幅度逐步由Vs下降为零。输出的Y电极驱动波形在这个时间段为:由Vs下降为零的斜坡.

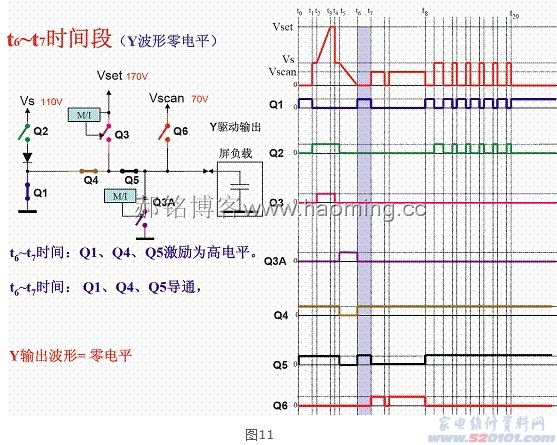

7、 t6~t7时间:这个时间段是输出零电平时间段 Y驱动波形;零电平

此期间;Y驱动组合开关电路工作状态如图11所示;电路的状态、过程和t0~t1时间段完全相同。

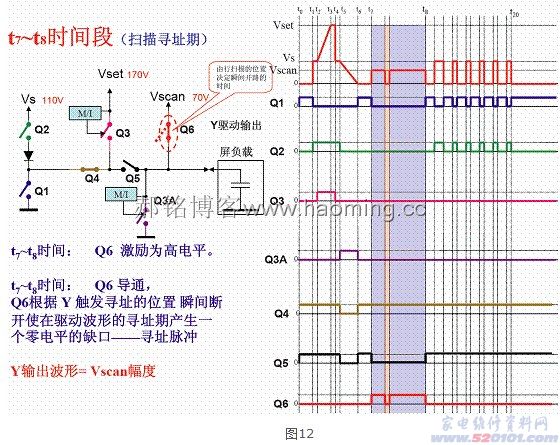

8、 t7~t8时间:这个时间段是寻址(也称扫描)时间段, Y驱动波形;在这个时间范围内是一个Vscan幅度的高电平,这个期间对应的地址驱动波形也是高电平(像素点亮);两者间电位差太小,不会引起Y电极和地址电极间的放电,在寻址瞬间;在Y驱动波形产生一个下凹的波形(负脉冲),在这一瞬间;Y电极为低电平地址电极为高电平,引燃触发放电产生。这个下凹的脉冲,随Y电极扫描位置的不同;在寻址期出现的时间不同。

在此时间段;Y驱动组合开关电路工作状态如图12所示;从图12的右边 t7~t8时间阴影部分可以看出,此时: Q4、Q6激励信号是高电平(Q6在寻址触发瞬间是低电平);对应左边的组合开关图中的开关;Q6闭合导通;虽然Q4也导通,但是由于Q5的断开Q4的导通无意义,也等效于只有Q6导通,其它的Q1、Q2、Q3、Q3A、Q5激励波形是低电平;对应左边的组合开关图中的开关;Q1、Q2、Q3、Q3A、Q5是断开状态。此时输出电平和波形;完全取决于Q6的工作状态;在这个寻址期Q6基本是闭合导通,由于Q6的供电是Vscan 所以;输出波形就是Vscan。在寻址触发瞬间Q6迅速断开又迅速导通,在这一瞬间在输出形成了一个下凹的脉冲波形。

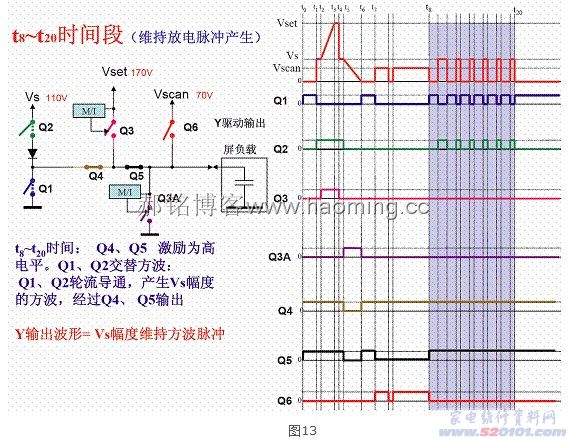

9、 t8~t20时间:这个时间段是维持放电时间段;输出的波形是Vs幅度的交流方波(在壁垒电荷的配合下,等离子放电腔体的放电持续维持下去)。

此期间;Y驱动组合开关电路工作状态如图13所示:从图13右边的 t8~t20时间阴影部分可以看出:可以看出Q4、Q5激励信号是高电平;Q4、Q5闭合导通,Q3、Q3A、Q6激励波形是低电平;Q3、Q3A、Q6断开,Q1、Q2激励信号是交替变换的方波;Q1、Q2是轮流导通;Q2导通瞬间Vs幅度的电压加到输出端,输出到屏负载的Y电极驱动波形在这个时间段为:Vs幅度的交流方波。

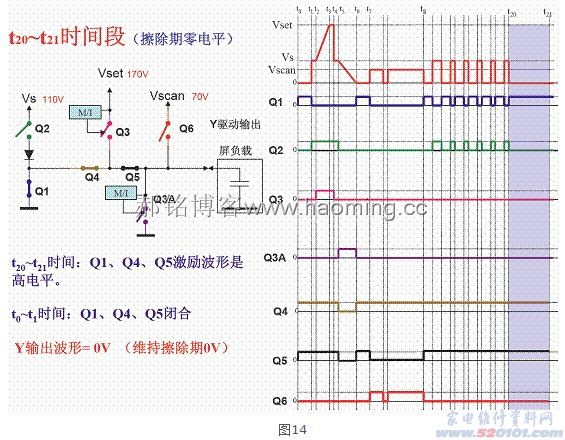

10、 t8~t20时间:这个时间段是擦除时间段 Y电极驱动波形是零电平,由X电极驱动电路产生擦除脉冲,进行壁垒电荷的清除工作,图14所示。

此时的电路及工作状态和t0~t1时间段相同。

以上是以简单的等效电路;介绍了等离子屏Y电极驱动波形产生的过程;可以看出等离子屏的Y电极驱动电路实际上就是一群开关的组合;实际电路是采用MOS管取代等效电路中的开关,电路的工作条件;1、就是要有组合开关的激励信号,2、要向电路提供精准的Vs、 Vset、 Vscan 电压。 激励信号是由等离子专用逻辑电路提供,精准的Vs Vset Vscan电压是由开关电源提供。[Page]

以上只是等效电路分析;实际电路要还有能量回复电路等要复杂的多,不过由浅入深、循序渐进掌握故障的维修是没有问题的。

学习等离子电视机原理及维修技术就是要掌握:等离子屏的结构、屏工作原理、X、Y驱动原理及逻辑驱动信号的产生原理,及复杂的等离子开关电源技术,这些掌握了经过一定时间的实践锻炼,就可以胜任等离子电视的工作了,可以断定;能进入完全胜任这个领域的是不多的,这才是机会。

后面要介绍 能量回复电路的原理、子场显示技术及逻辑驱动电路原理

X电极驱动电路原理类似上面介绍的原理,要简单的多,希望有志者能根据前面所画的X电极驱动波形,自行设计一个类似前面Y驱动波形产生过程的;产生X驱动信号的开关等效电路图,能行吗?试试好吗?